DFT(テスト容易化設計)概要TestWay / Testway Express

DFT(テスト容易化設計/Design For Test)

TestWay/TestWay Expressは、実装基板のレイアウト図/ネットリスト/回路図/部品リストをインポートするだけで、 デザインルールチェック、テストカバレッジ予測や各種テスタ用ファイルを自動生成し、各種テストプログラム開発の効率化と最適化を行います。製品の設計段階で、JTAG/バウンダリスキャン、FPT(フライングプローブテスタ)、ICT(インサーキットテスタ)、AOI,

AXI 及びファンクションテストが効率的に行えるように、事前に回路を最適化することにより、テスタビリティ (テスト可能な範囲)を飛躍的に向上させることが可能な、テスト容易化設計支援ソフトです。

また、JTAGやフライングプローブテスタなどとの組み合わせによる、テストカバレッジを素早くシミュレーションすることが可能です。改善されたテストカバレッジはテスト・コストを削減し、製品の信頼性向上に大きく貢献します。

1.どのように動作するのか ?

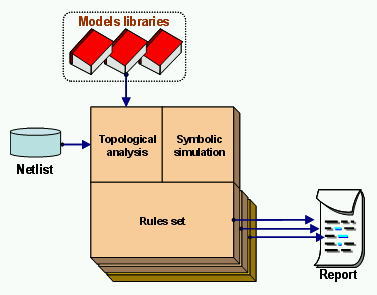

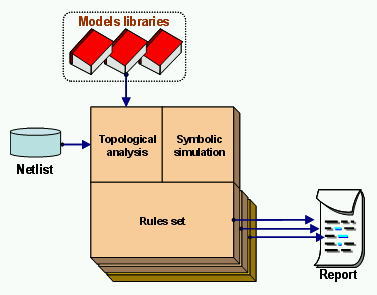

TestWay/TestWay Expresはネットリストおよびモデル・ライブラリを読み取り、テスタビリティ向上のための設計改善個所をレポートします。 その他に、TestWayは、 テスタビリティ、信頼性、各社JTAG/バウンダリスキャン・ソリューション用ファイルの自動生成、コスト計算やフィクチャ・デザインに役立つレポートファイル等の価値ある統計データを自動生成します。 TestWayは、ネットリスト、回路図およびレイアウト情報のために34種類以上のCADファイル・フォーマットを取り込むことが可能です。

TestWayフレームワーク

2.ビルトインとカスタムルール

TestWayのデザイン・ルール・セットは各規格に由来し、エレクトロニクス産業で一般に適用されたルールを含んでいます。

デザイン・ルール

デザインルール(Open-collector, Open-emitter, HCMOS等)に適合しているかを確認します。

インサーキット・テスト法

パテショニングと初期設定ピンコントロール (SET-RESET, Chip select, Output enable, Test)を保証します。

バウンダリスキャンテスト法

バウンダリスキャン・パスの接続性およびテスト・バス他をチェックします。

下記の例では、TDIにプルアップ抵抗が欠けていることを示しています。

JTAGチェーンの表示例

カスタム・ルール

お客様のルールを定義しTestWayに統合することが可能です。

3.テスト・ポイント・セイバー

PCBのデバイス密度の劇的な増加につれて、ネット各々に完全にアクセスするのは非常に困難です。 異なるテスト・アプローチ (*AOI, AXI, BST, FCT, FPT, ICT…)を評価し、TestWayは必須のテスト・アクセスの数を最大化します。

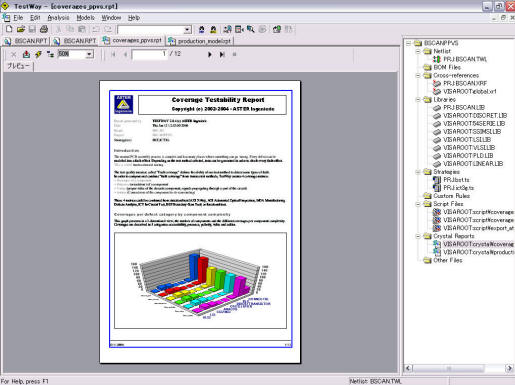

4.カバレージ予測

TestWayは、利用可能な物理的・仮想テスト・ポイントに基づいたテストカバレッジを評価・予測することができます。 これは回路図の段階あるいはレイアウト中に可能となります。そのため、設計図がテスト部門に達する前に、アクセスを改善することが出来ます。

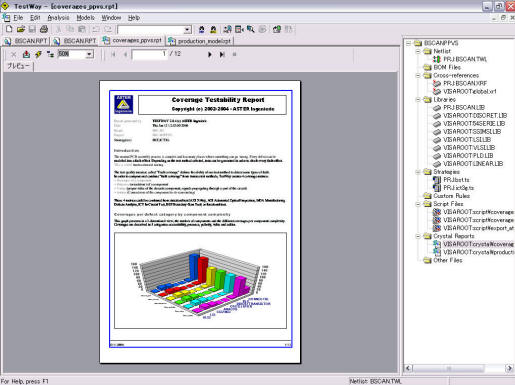

テストカバレッジレポート例

5.テストインターフェイス(テストプログラム開発用ファイルセットの自動生成)

TestWay Expressは、以下に示すテスタのための入力ファイルを自動生成します。

対応機種例:

Pick and Place:EUROPLACER、FPIP2、など

AOI/AXI:CYBEROPTICS、MIRTEC、SAKI、TR7500、BFX2、OPTICON(Goepel)など

JTAG/BSCAN:ASSET、CORELIS、CASCON(Goepel)、JTAG Tec,など

FPT:TAKAYA、SPEAなど

ICT:TERADYN L200, GR228x, Z1800, Agilent i3070 など

6.コンカレント・エンジニアリングの利益

1.どのように動作するのか ?

TestWay/TestWay Expresはネットリストおよびモデル・ライブラリを読み取り、テスタビリティ向上のための設計改善個所をレポートします。 その他に、TestWayは、 テスタビリティ、信頼性、各社JTAG/バウンダリスキャン・ソリューション用ファイルの自動生成、コスト計算やフィクチャ・デザインに役立つレポートファイル等の価値ある統計データを自動生成します。 TestWayは、ネットリスト、回路図およびレイアウト情報のために34種類以上のCADファイル・フォーマットを取り込むことが可能です。

TestWayフレームワーク

2.ビルトインとカスタムルール

TestWayのデザイン・ルール・セットは各規格に由来し、エレクトロニクス産業で一般に適用されたルールを含んでいます。

デザイン・ルール

デザインルール(Open-collector, Open-emitter, HCMOS等)に適合しているかを確認します。

インサーキット・テスト法

パテショニングと初期設定ピンコントロール (SET-RESET, Chip select, Output enable, Test)を保証します。

バウンダリスキャンテスト法

バウンダリスキャン・パスの接続性およびテスト・バス他をチェックします。

下記の例では、TDIにプルアップ抵抗が欠けていることを示しています。

JTAGチェーンの表示例

カスタム・ルール

お客様のルールを定義しTestWayに統合することが可能です。

3.テスト・ポイント・セイバー

PCBのデバイス密度の劇的な増加につれて、ネット各々に完全にアクセスするのは非常に困難です。 異なるテスト・アプローチ (*AOI, AXI, BST, FCT, FPT, ICT…)を評価し、TestWayは必須のテスト・アクセスの数を最大化します。

4.カバレージ予測

TestWayは、利用可能な物理的・仮想テスト・ポイントに基づいたテストカバレッジを評価・予測することができます。 これは回路図の段階あるいはレイアウト中に可能となります。そのため、設計図がテスト部門に達する前に、アクセスを改善することが出来ます。

テストカバレッジレポート例

5.テストインターフェイス(テストプログラム開発用ファイルセットの自動生成)

TestWay Expressは、以下に示すテスタのための入力ファイルを自動生成します。

対応機種例:

Pick and Place:EUROPLACER、FPIP2、など

AOI/AXI:CYBEROPTICS、MIRTEC、SAKI、TR7500、BFX2、OPTICON(Goepel)など

JTAG/BSCAN:ASSET、CORELIS、CASCON(Goepel)、JTAG Tec,など

FPT:TAKAYA、SPEAなど

ICT:TERADYN L200, GR228x, Z1800, Agilent i3070 など

6.コンカレント・エンジニアリングの利益

- 設計者が修正を絶え間なく行ない、テスタビリィティ問題を常に確認することによるより、高いテスト・カバレージを実現。

- 最適のテスト・ポイントの識別によるより高いテスト・カバレージおよび 回路図に注釈を表示します。

- レイアウトに先立ってテスト・ポイントを割り当てることができるので、レイアウト時間の短縮が可能。

- より少ないテスト・ポイントでフィクチャ・コストを低下させることが可能。 回路図の段階で多くのテスト問題を解決することができ、より早いマーケットへの投入が可能。

- レイアウトに先立って実質的にテスト・プログラムを開発することができ、より速い時間でマーケットへ投入が可能。

- Windows 7、8、.UNIX (SunOS , SOLARIS, and HP-UX )対応